Kategorien

Kategorien

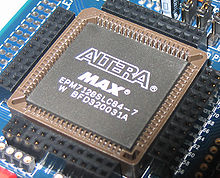

CPLD steht für Complex Programmable Logic Device. Die Technologie programmierbarer ICs ist seit den 60er Jahren bekannt, als Harris Semiconductor einen Baustein herausbrachte, dessen wesentlicher Bestandteil eine programmierbare Diodenmatrix (Fuse Configurable Diode Matrix) war. 1978 kamen die ersten vollständig konfigurierbaren Logikbausteine namens PLA (Programmable Logic Array) mitsamt Programmiersprache PALASM auf den Markt.

CPLDs bestehen im Wesentlichen aus folgenden Elementen:

CPLDs bestehen im Wesentlichen aus folgenden Elementen:

Ein-/Ausgabeblöcke können schnelle Speicher, wie Latches, D-Flipflops oder Register, sein. In vielen modernen PLDs stehen programmierbare Ausgänge zur Verfügung, denen man definierte Zustände (active low, active high, tristate) zuweisen kann. Der AND/OR-Matrix als Kern kann jede beliebige kombinatorische Verknüpfung zugewiesen werden.

Oft werden CPLDs mit den digitalen und ebenfalls rekonfigurierbaren FPGA-Bausteinen (Field Programmable Gate Array) gleichgesetzt bzw. verglichen. Die wesentlichen Unterschiede zwischen FPGAs und CPLDs sind: