DMA

|

|

erstmal nur Text-Sammlung zum Thema !! auch Aufteilung auf Allgeine / PIO / DMA -Seiten ?!? denkbar |

Diese Technik erlaubt angeschlossenen Peripheriegeräten, wie Netzwerkkarte oder Soundkarte, ohne Umweg über die CPU direkt mit dem Arbeitsspeicher zu kommunizieren. Der Vorteil des Speicherdirektzugriffs ist die schnellere Datenübertragung bei gleichzeitiger Entlastung des Prozessors.

Direkter Speicherzugriff Die konventionelle Methode, Daten von einer Eingabe-Ausgabe-Einheit in den Arbeitsspeicher zu transferieren, nutzt Prozessorregister zur Zwischenspeicherung. Erst werden die Daten vom Prozessor in sein internes Register eingelesen, um dann in einem weiteren Schritt in den Arbeitsspeicher verschoben zu werden. Dafür sind viele Taktschritte notwendig, in denen der Prozessor nicht für die Ausführung anderer Befehle zur Verfügung steht, und somit wird die Ausführungsgeschwindigkeit laufender Programme verringert. Ein-/Ausgabe über direkten Speicherzugriff

Der direkte Speicherzugriff ist eine Schaltungs- und Steuermaßnahme, die über spezielle Datenleitungen auf dem Motherboard eine Verbindung zwischen Steckkarten (oder auch I/O auf dem Motherboard selbst) und dem Arbeitsspeicher herstellt. Dadurch können die Daten ohne Umweg über den Prozessor direkt in den Speicher geschrieben werden, und die Ausführungsgeschwindigkeit laufender Programme wird nicht beeinflusst.

Beim PC gibt es nur eine reale DMA-Leitung. Der Zugriff der unterschiedlichen Komponenten (Steckkarten) wird anhand eines Index unterschieden. Demnach darf ein DMA-Index nur einem Gerät zugeordnet werden. Der Index gibt die Nummer des DMA-Kanals an. Insgesamt gibt es 8 DMA-Kanäle. Die Kanäle 0, 2 und 4 sind für interne Zwecke bereits fest vergeben. Die Kanäle 1, 3, 5, 6 und 7 können frei belegt werden. Die Kanäle 0–3 arbeiten mit 8, die Kanäle 4–7 mit 16 Bit.

Funktionsweise des DMA-Controllers

In modernen Chipsätzen ist der DMA-Controller (DMA-C) integriert. Ältere Motherboards haben einen separaten Baustein wie zum Beispiel den 8237 von Intel.

Will die I/O-Hardware Daten senden oder empfangen, trennt der DMA-Controller den Prozessor vom Bussystem. Der DMA-Controller führt dann die Anforderung mit hoher Geschwindigkeit aus. Danach wird die Verbindung zwischen Prozessor und Bussystem wieder hergestellt. Für den Speichertransfer benötigt der Prozessor bis zu 40 Takte je Byte. Der DMA-Controller führt den Zugriff innerhalb von vier Takten aus.

Der DMA-Controller dient zum Datentransport zwischen Arbeitsspeicher und Peripherie. Dies führt zu einer Entlastung des Prozessors. Neben einem Geschwindigkeitszuwachs bei speicherintensiven Anwendungen ermöglicht die Verwendung von DMA-Controllern außerdem sehr hohe Datenraten z. B. beim Brennen von DVD-Medien. Selbst mit aktuellen PC-Systemen sind Brenngeschwindigkeiten von 16× ohne DMA-Unterstützung nicht möglich.

Arbitrierung

Der DMA-Controller muss die Daten zwangsläufig über dieselben Daten-, Adress- und Steuerleitungen des jeweiligen Bussystems übertragen (lassen) wie sonst die CPU. Es muss also dafür gesorgt werden, dass CPU und DMA-Controller nicht kollidieren. Dazu wird im Voraus eine „Arbitrierung“ durchgeführt, ein Verfahren, bei dem der DMA-Controller die Kontrolle über die Busse bei der CPU anfordert, letztere dies bei nächster Gelegenheit gewährt und dann die Busse freigibt. Nach Abschluss des DMA-Transfers wird die Busanforderung wieder zurückgenommen, und die CPU kann wieder übernehmen.

Elektrisch gibt es dazu verschiedene Implementierungen, mit verschiedenen Anzahlen von Steuerleitungen. Die ausführlichste und damit überschaubarste Variante verfügt über eine Bus-Request-Leitung (Anforderung) vom DMA-Controller zur CPU sowie eine Bus-Grant-Leitung (Gewährung) in umgekehrter Richtung.

noch einer

Zeitverhalten der Übertragungs-Modi Die ATA-Spezifikation legt drei grundlegende Übertragungsprotokolle für die IDE-Schnittstellen fest. Es sind der PIO-Mode 0 bis 4, der Multiwort-DMA 0 bis 2, und der UltraDMA 0 bis 4, wobei 3 für UltraDMA/33, 4 für UltraDMA/66 und 5 für UltraDMA/100 steht. Die PIO-Modi benötigt die CPU, um Daten von der Festplatte in den Arbeitsspeicher zu übertragen. Beim DMA- und UltraDMA-Transfer erfolgt der Datenaustausch über das PCI-Busmastering ohne zutun der CPU. So ergibt sich zwangsläufig der Vorteil einer geringeren CPU-Belastung im DMA-Modus. Ein Vorläufer des Multiwort-DMA-Modus ist Einzelwort-DMA-Mode. Er funktioniert ähnlich, kann jedoch pro Transfer nur ein statt mehrerer Datenworte hintereinander übertragen. Multiwort-DMA hat Einzelwort-DMA abgelöst und spielt heute keine Rolle mehr. In den folgenden Kapitel werden die zeitlichen Abläufe der wichtigsten Modi erläutert.

PIO-Modus

| Mode | 0 | 1 | 2 | 3 | 4 |

| PIO-Zykluszeit [ns] | 600 | 383 | 240 | 180 | 120 |

| Datenrate [MByte/s] | 3,3 | 5,2 | 8,3 | 11,1 | 16,6 |

Einzelwort-DMA-Modus

| Mode | 0 | 1 | 2 |

| Einzelwort-DMA-Zyklus [ns] | 960 | 480 | 240 |

| Datenrate [MByte/s] | 2,1 | 4,2 | 8,3 |

Multiwort-DMA-Modus

| Mode | 0 | 1 | 2 |

| Multiwort-DMA-Zyklus [ns] | 480 | 150 | 120 |

| Datenrate [MByte/s] | 4,2 | 13,3 | 16,6 |

Ultra-DMA-Modus

| Mode | 0 | 1 | 2 | 3 | 4 | 5 |

| Ultra-DMA-Zyklus [ns] | 240 | 160 | 120s | 90 | 60 | 40 |

| Datenrate [MByte/s] | 16,6 | 25,0 | 33,3 | 44,4 | 66,6 | 100 |

Welche Betriebsarten der Kontroller unterstützt, ist in der Parameterliste des Kommandos IDENTIFY DRIVE festgelegt. In den aufgeführten Tabellen sind alle Modi in Bezug auf Zykluszeit und maximaler Datentransferrate aufgeführt. Als Umrechnungsbasis sind 1000 Bit = 1 KByte festgelegt.

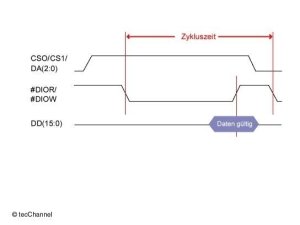

Der PIO-Mode steuert alle Zugriffe auf die Kontrollregister: das Setzen aller relevanten Parameter, das Schreiben von Kommandos und Lesen der Fehler- und Statusinformationen. Selbstverständlich erfolgen auch alle Schreib- und Lesezugriffe auf das Datenregister in diesem Modus. Bild 1 stellt einen vereinfachten PIO-4-Datentransfer mit einer Zykluszeit von 120 ns dar.

Für eine PIO-4-Datenübertragung muss der Host die Adressleitungen DA(2:0) und die Chipselect-Leitungen CS0, CS1 zuerst auf High legen. Nach mindestens 25 ns signalisiert er dann dem Laufwerk durch Setzen der Leitung #DIOR einen Lesezugriff oder durch #DIOW einen Schreibzugriff. Da ein Datentransfer immer im 16-Bit-, und ein Registerzugriff im 8-Bit-Modus erfolgt, ist eine zusätzliche Leitung (unter ATA-1 #IOCS16-Leitung) nicht mehr erforderlich. Bei einem Lesezugriff legt der Kontroller, und bei einem Schreibzugriff der Host die Daten auf die Transferleitungen. 70 ns nach Setzen der Schreib- oder Leseleitung erfolgt vom Empfänger mit der negativen Flanke des #DIOx-Signals die Übernahme der gültigen Daten. Der Schreib-/Lesezyklus wird nach mindestens 25 ns durch Freigeben der #DIOR und #DIOW Signalleitungen beendet.

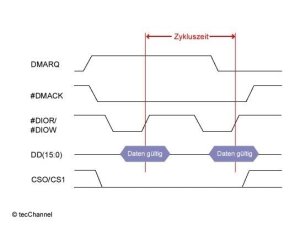

Multiwort-DMA Im Gegensatz zum Einzelwort-DMA bringt erst der Multiwort-DMA die Vorteile der niedrigeren CPU-Belastung durch den direkten Speicherzugriff. Bei Einzelwort-DMA muss der Prozessor den Transfer jedes Datenwortes einzeln initialisieren. Das kostet Systemleistung. Der Datentransfer über Multiwort-DMA benötigt nur eine Initialisierungsroutine der CPU für die Übertragung mehrerer Datenworte. Der Kontroller übernimmt dann den Datenaustausch in den Systemspeicher. Bild 2 zeigt einen Lesezugriff im Multiwort-DMA Mode 2 mit einer Zykluszeit von 120 ns.

Der Host setzt die DMARQ-Leitung und signalisiert damit dem Laufwerk, dass es einen DMA-Zugriff durchführen will. Das Gerät beantwortet diese Anfrage, indem es die #DMACK-Leitung und die Chip-Select-Leitungen (CSx) auf Low legt. Darauf antwortet der Host mit dem Setzen des Lesesignals #DIOR. Nach 70 ns können die gültigen Daten mit der negativen Flanke der Leseleitung übernommen werden. Ein weiterer Lesezugriff kann nach 25 ns durch erneutes Setzen der #DIOR Leitung erfolgen. Beim letzten DMA-Transfer nimmt der Host, während #DIOR High ist, das DMARQ-Signal weg und signalisiert dem Laufwerk, dass es den DMA-Lesezugriff beenden will. Dies quittiert das Gerät mit einem High auf der #DMACK-Leitung, nachdem es zirka 5 ns zuvor den letzen Lesetransfer durchgeführt hat.

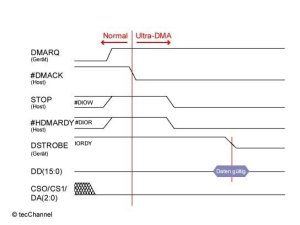

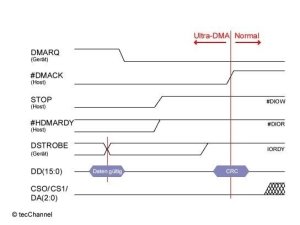

UltraDMA Abhängig von der Datenrichtung gibt es zwei verschiedene Bezeichnungen für den UltraDMA-Transfer. Der UltraDMA-Data-In-Burst bezeichnet einen Lesezugriff (vom Host aus gesehen) und der UltraDMA-Data-Out-Burst einen Schreibzugriff. Für beide Datentransfer unterscheidet man vier Betriebsphasen: Initialisierung, Transfer, Pause und Ende. Um diese Vorgänge zu verdeutlichen, dient ein Lesezugriff als Beispiel. Die Initialisierungsphase Die Initialisierungsphase beginnt, indem das Gerät vom Host durch Setzen des Signals DMARQ einen UltraDMA-Lesezugriff anfordert. Kurz darauf muss #DIOW und #DIOR auf High, CS0, CS1 und DA(2:0) auf Low gehen. Erwidert jetzt der Host den Lesezugriff mit dem Setzen der #DMACK-Leitung, ändern sich die Bezeichnung und die Bedeutung einiger Leitungen wie im Bild 3 dargestellt. Nach einer Umschaltzeit von 20 bis maximal 55 ns wechseln die neu bezeichneten Signalleitungen STOP und #HDMARDY ihren Zustand. Nach maximal 90 ns (Mode 5) wird die DSTROBE-Leitung auf Low gelegt. Mit diesem Vorgang werden die ersten gültigen Daten vom Host eingelesen.

Die Initialisierungsphase ist damit abgeschlossen, der UltraDMA-Data-In-Burst beginnt.

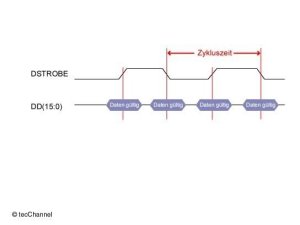

Die UltraDMA-Burst-Phase Bild 4 zeigt in vereinfachter Form den Ausschnitt eines UltraDMA-Bursts. Man kann deutlich erkennen, dass im Gegensatz zum PIO-Modus oder Multiwort-DMA, mit jeder Taktflanke des #DSTROBE-Signals Daten eingelesen werden. Da UltraDMA jede fallende und steigende Flanke zur Datenübermittelung nutzt, spricht man auch von Double Edge Clocking. Bei einer Zykluszeit von 40 ns (UltraDMA/100), das entspricht einer Frequenz von 25 MHz, erfolgen zwei 16-Bit-Datenzugriffe. Daraus resultiert eine theoretische Übertragungsgeschwindigkeit von 800 MBit/s, dass entspricht 100 MByte/s (Basis: 1000 Bit = 1 KByte).

Das Verfahren, beide Taktflanken zu nutzen, setzt sich auch immer mehr in anderen Bereichen wie Grafikkarte und Speicher durch.

Die UltraDMA-Pause Der Host oder das Gerät können für einen bestimmten Zeitraum auch ein UltraDMA-Burst unterbrechen (paused). Der jeweilige Initiator legt dazu das Signal #DMARDY auf High. (Host: #HDMARDY, Gerät: #DDMARDY). Danach sendet das Gerät für die Dauer der Pause einfach kein STROBE-Signal. Das Aufheben der Pause geschieht durch erneuten Signalwechsel der #DMARDY-Leitung. Die Taktung der STROBE-Leitung wird daraufhin wieder aufgenommen und somit der Burstzyklus fortgesetzt.

Das Ende einer UltraDMA-Burst-Phase Wie ein Laufwerk einen Datentransfer im UltraDMA-Mode beendet, verdeutlicht das Zeitdiagramm in Bild 5. Nach der Übertragung des letzen Datenwortes mit einem Flankenwechsel des DSTROBE-Signals legt das Gerät 50 ns später die DMARQ-Leitung auf Low. Es signalisiert somit dem Host, dass er den Burstzyklus beenden soll. Der Host quittiert dies mit dem Setzen des STOP-Signals und mit dem High-Pegel auf der #HDMARDY-Leitung. Kurz darauf setzt der Host #DMACK auf High und schließt somit den Burstzyklus ab. Die ursprünglichen Bedeutungen und Bezeichnungen der Signale (wie im PIO-Modus) sind wieder gültig und ein neuer Datentransfer kann erfolgen.

Eine wichtige Neuerung ist mit Einführung der UltraDMA-Modi 0 bis 5 hinzugekommen. Am Ende eines jeden UltraDMA-Bursts wird eine Fehlererkennung des übertragenen Datenstroms durchgeführt. Durch diese CRC-Prüfsumme erhöht sich die Sicherheit der Datenübertragung enorm. Der Host sowie das Gerät berechnen nach einem im ATA-4 festgelegten Algorithmus (G(X)=X16+X12+X5+1) die CRC-Prüfsumme. Dieser Algorithmus ist in der Elektronik implementiert. Am Ende eines jeden Datenbursts sendet der Host die Prüfsumme an das Gerät. Das Gerät überprüft die beiden Prüfsummen. Ist ein Fehler aufgetreten, wird der fehlerhafte Datenburst nochmals übertragen. Treten jedoch massive Fehlerhäufungen auf, schaltet der Host auf einen langsameren UltraDMA-Modus um. Dieser Vorgang läuft unabhängig vom Prozessor. Diese Art von Fehlererkennung durch eine Polynomberechnung ist gegenüber einer einfachen Parity-Bit-Prüfung, wie sie bei der SCSI-Schnittstelle zur Verwendung kommt, wesentlich sicherer.

Links

- zu Nachweisquellen

- zu Dokumentationen